# **Active Extenders**

PCIAX CPCI64

Hot Swap PCI Bus Extender Boards

**PCI**

User Manual Revision 5.3 September, 2000

1439 Torrington Court San Jose, CA 95120

Tel: (408) 268-4145 Fax: (408) 268-8280

www.catalyst-ent.com

Email: <a href="mailto:support@catalyst-ent.com">support@catalyst-ent.com</a>

© 1996-2000

P/N 400-0015-001

# **TABLE OF CONTENTS**

| INTRODUCTION                       | 3        |

|------------------------------------|----------|

| INSTALLATION                       |          |

| OPERATION                          | 4        |

| ON-OFF                             | 4        |

| PCIAX                              |          |

| CPCI-64                            |          |

| POWER-ON RESET                     | 5        |

| CURRENT MEASUREMENT                | 5        |

| CURRENT LIMIT CIRCUITRY            | 5        |

| CURRENT LIMIT ADJUSTMENT           | 5        |

| EXTERNAL POWER SUPPLY              | <i>.</i> |

| JUMPERS TABLE                      |          |

| LED TABLE                          | 8        |

| LEDs                               | 8        |

| 3.3V INPUT                         |          |

| 5V=>3V TRANSLATION                 | 8        |

| SPECIFICATION: PCIAX532 & PCIAX332 | 9        |

| SPECIFICATION: CPCI-64             | 10       |

| BOARD LAYOUT, PCIAX                | 11       |

| BOARD LAYOUT, CPCI-64              | 12       |

### INTRODUCTION

These Active Extender boards allow HOT SWAPPING or LIVE INSERTION of the Unit-Under-Test into PCI (CompactPCI for CPCI-64) bus. The "HOT SWAPPING" feature of these extenders eliminates the need for turning the PC Off and On and repeated rebooting. This feature speeds up rework, characterization and test of Unit-Under-Test in the development phase, as well as production test. The elimination of the repeated power cycling also helps prolong the system life and the hard disc operation. These Active Extenders use a new CMOS technology (known as "Quick Switch") for switching the signals On and Off. These switches have feature a very low propagation delay, typically about 250 picoseconds, resulting in no timing degradation between the bus and the Unit-Under-Test. The switches are also bi-directional allowing the entire address range to be supported for both target and master type operation.

These Active Extender boards isolate all signals and voltages to the Unit-Under-Test, when the On-Off switch is in the Off position. All voltages are ramped down and ramped up during the power down and power up in order to eliminate any spikes. During the power down the signals to the bus become isolated as soon as the main supply, +5V, falls to +3.0V. During the power up the signals stay isolated until the main voltage is at least +3.0V.

CPCI-64 and PCIAX Rev B and higher extender boards also allow voltage margin testing of the UUT, by allowing external power supplies to replace the system power supplies as inputs to the Unit-Under-Test.

On-board current-to-voltage converters allow measurement of the current drawn by the UUT at any time, using a voltmeter attached at the appropriate test points.

### INSTALLATION

To install the Active Extender board, make sure to turn the PC power off. Insert the Active Extender in any available slot and secure its bracket to the main chassis. You are now ready to use your new extender board.

NOTE: If you are planning to use an external I/O signal to control the board, the On-Off switch must be in the Off position.

## **OPERATION**

Using these Active Extender boards is no different than using a regular extender board, except that the Active Extenders boards offer several extra features. These are explained below:

#### **ON-OFF**

To insert or remove a Unit-Under-Test while system power is on, make sure that the Active Extender is turned Off. There are two ways to turn the Active Extender power On and Off. 1) The mechanical toggle switch on the card. 2) The external control signal.

### **PCIAX**

PCIAX boards may be controlled via a parallel port interface. Turn the On-Off switch to the Off position, plug a parallel cable between the system port and the board(s) and use the system parallel port address to turn the board(s) On and Off.

Several PCIAX Rev B (and higher) boards in the same system may be controlled independently, if so desired. Jumper J6 on the board may be used to configure each board to be turned On and Off by a different bit of the parallel port. For example, board One may be set to be controlled by D0 and board Two may be set to be controlled by D1. A Low level for each bit will turn the board On and High will turn the board Off. While in the software control mode, the PCIAX will power up in the OFF state, when the computer is first booted. In order to control the PCIAX using software command:

Assuming the system parallel port address is set at 378:

| outp (0x378, 0xFF) | Will turn all boards Off    |

|--------------------|-----------------------------|

| outp (0x378, 0x80) | Will turn only board one On |

| outp (0x378, 0x81) | Will turn only board two On |

### CPCI-64

The external control input for the CPCI is at JPX. Top signal is a Ground signal and the bottom signal is the control signal. To control On-Off by the external signal, you must have the mechanical switch in the Off position. A Low level, less than 1.5V, will turn the board ON. Revision B and higher CPCI-64, supports Global Address signals (GA0 – GA4).

NOTE: During the power Off, all signals become isolated between the bus and the Unit-Under-Test when the +5V to the Unit-Under-Test becomes less than 3.0V.

NOTE: If you are running software that relies on a response from the Unit-Under-Test, do not turn off the Active Extender board unless the handshaking has taken place, Otherwise you may experience a system hang-up. It may be a good practice to stop the software from running, before isolating the power and the signals to the Unit-Under-Test.

### **POWER-ON RESET**

Each time the Active Extender board is turned Off and then On, a reset signal will be generated from the extender to the Unit-Under-Test automatically. The duration of this reset is 200 milliseconds. The reset to the Unit-Under-Test is also activated every time there is a reset from the bus.

#### **CURRENT MEASUREMENT**

To measure the current being drawn by the Unit-Under-Test, just connect a voltmeter to J3. Every Volt read by the meter represents One Amp, so a voltmeter reading of 0.35 indicates that the Unit-Under-Test is drawing 350 milliamperes of current. J3 terminals are marked for Ground, +5I, +3.3I and +12I.

NOTE: If the VIO and +5V are on the same plane on your board, you need to remove the JP10 jumper from the extender board, in order to get an accurate current measurement for the +5V.

### **CURRENT LIMIT CIRCUITRY**

Red LEDs, when illuminated, indicate a short or a very low voltage. Green LEDs when illuminated, indicate voltages at their designated outputs. In the case of the short for the +5V, +12V and +3.3V from the Unit-Under-Test, the Active Extender will automatically switch the current limit down to about 200 milliampere and will continue to deliver this current for troubleshooting purposes. In the case of shorts or excessive current draw for the other voltages, resetable fuses will open up until the problem is corrected.

The current limit value for the +5V is set to 5 Amps with JP8 (JP2 for CPCI) not installed and 1 Amp with JP8 (JP2 for CPCI) installed.

# CURRENT LIMIT ADJUSTMENT FOR PCIAX532/PCIAX332

To increase the +5V current limit you must remove the resistor at R23 and perform the following reworks:

- To change the current limit to 8A install a 10k resistor at location R22 and a 6.2k resistor at location R23. This does not affect the current measurement reading.

- To change the current limit to 10A, install a 10k resistor at location R22 and R23. This does not affect the current measurement reading.

To increase the +3.3V current limit, you must supply +3.3V current from the motherboard or an external power supply and reduce the gain of the current measurement circuitry. To do so, perform the following rework:

• To change the current limit to 8A install a 4.7k Resistor on top of R57. This does not affect the current measurement reading.

#### **FOR CPCI-64**

To increase the +5V current limit you must remove the jumper/resistor at R32 and perform the following reworks:

- To change the current limit to 8A install a 10k resistor at location R32 and a 6.2k resistor at location R22. This does not affect the current measurement reading.

- To change the current limit to 10A install a 10k resistor at location R32 and R22. This does not affect the current measurement reading.

To increase the +3.3V current limit, you must supply +3.3V current from the motherboard or an external power supply. Perform the following rework:

To change the current limit to 8A install a 4.7K Resistor on top of R36. This does not affect the current measure reading.

### **EXTERNAL POWER SUPPLY**

This feature is not supported by PCIAX Rev A. There are no jumpers on the PCIAX Rev A board to re-configure for the external supply.

An external terminal J5 is used for the external power supply input. However, remember never to connect any supply to these inputs so long as you have JP4, JP5, JP6 and JP7 installed. If you want to use the external supply as an input, you must remove these 4 jumpers to avoid any conflict with the bus voltages. These jumpers are, however, independent from each other. For instance if you would want to bring in only a +5V from the external supply and continue to use the bus voltages for +12V, -12V, and +3.3V, you would only need to remove JP5. The list below matches each jumper to its supply:

JP4 = -12V

JP5 = +5V

JP6 = +12V

JP7 = +3.3V

JP7 1-2 for 3.3V from on-board regulator, JP7 2-3 from the bus, not installed from the external supply

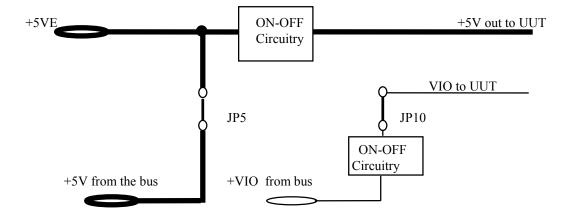

The following diagram indicates the interconnection of the Unit-Under-Test voltages to the bus voltages and the external voltages:

As you can see, there will be conflict in case the external supply is connected while the jumper is still in place. This circuit is repeated for each of the 4 voltages, with the exception of the Auxiliary circuit.

If you are using external power supplies do not forget to connect the Ground (GND) signals between the system and the supply. If your external power supply outputs are not isolated, make sure the ground of the PC (containing the extender board) and the ground of the power supply are at the same voltage phase/level with respect to a common point, before connecting the GND signal.

If making current measurements on +5V, be sure to remove JP10 if the VIO and +5V on your board are on the same voltage plane.

### **JUMPERS TABLE**

| Description                                         |               | Jumper                    | Utilization                                                                                                                                    |

|-----------------------------------------------------|---------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| External power input                                |               | J5                        | Inputs from external power supply                                                                                                              |

| Current measurement                                 |               | Ј3                        | Outputs to DVM                                                                                                                                 |

| -12V isolation from the syst                        | tem           | JP4                       | On = voltage from system, Off = from Ext. supply                                                                                               |

| +12V isolation from the sys                         | stem          | JP6                       | On = voltage from system, Off = from Ext. supply                                                                                               |

| +5V isolation from the syste                        | em            | JP5                       | On = voltage from system, Off = from Ext. supply                                                                                               |

| +VIO connection to the syst<br>through the extender | tem           | JP10                      | On = VIO from the system Off = from UUT plane If this jumper is removed the UUT VIO signals must be connected to the main voltage plane.       |

| 3V ⇔ 5V translation                                 |               | JP3                       | Off = $3V$ translated, On = bus signals up to $5V$                                                                                             |

| 3.3V source                                         |               | JP7                       | On-board = Between 1 & 2 From system = 2 & 3 Square pad on the 3 pin jumper is pin 1                                                           |

| +5V current limit to 1 Amp                          |               | JP8 (PCIAX)<br>JP2 (CPCI) | On = 1A, Off = 5A<br>On = 1A, Off = 5A                                                                                                         |

| Remote On-Off                                       | CPCI<br>PCIAX | JPX (CPCI)<br>J6 (PCIAX)  | On < 1.5V at the bottom terminal (pin 2)<br>Shunt on SW, control On-Off by switch.                                                             |

|                                                     |               |                           | Shunt on DB0, control On-Off by bit 0 of parallel port. On DB1 by bit 1 of parallel port DB6 by bit 6. See ON-OFF under the operation section. |

# **LED TABLE**

| LED Purpose   | PCIAX532/PCIAX332 | CPCI-64 |

|---------------|-------------------|---------|

| +5V Present   | D12               | D15     |

| +12V Present  | D11               | D4      |

| -12V Present  | D10               | D3      |

| VIO Present   | D18               | D9      |

| +3.3V Present | D13               | D5      |

| +5V Problem   | D16               | D7      |

| +12V Problem  | D15               | D11     |

| -12V Problem  | D9                | D2      |

| +3.3V Problem | D14               | D6      |

### **LEDs**

There are two sets of LED on the board, green and red. Each LED has a label which voltage it represents. The green LED, when lit, indicates presence of the corresponding voltage. The red LED, when lit, represent a short on the corresponding voltage. Please note that the green LEDs do not indicate if the voltage is at the expected level or not.

### **3.3V INPUT**

These Active Extender cards have an on-board 3.3 Volt regulator (PCIAX Rev B and higher).

JP7 selects the source of the 3.3V to the UUT.

JP7 1-2 3.3V from the on-board regulator.

JP7 2-3 3.3V from the system bus.

JP7 no shunts 3.3V from the external supply.

# **5V=>3V TRANSLATION**

These Active Extender cards are capable of translating the incoming 5-Volt signals to 3.3 Volts for the UUT without any timing degradation. Therefore cards or components needing a 3-Volt environment can be tested or operated on a 5-Volt system using these extender cards.

With JP3 installed the UUT signals will be the same as the bus signals, most likely 5V. When JP3 is not installed, the signals to the UUT will be translated down to 3.3V.

SPECIFICATION: PCIAX532 & PCIAX332

**Bus:** PCIAX-532, 32-bit PCI, 5V key and universal.

PCIAX-332, 32-bit PCI, 3V key and universal.

Voltages:

Input requirement +5V at 200 mA, +/- 12V at 50 mA.

Inputs From PC bus or the external input, configurable by jumpers per

voltage. (For Rev B boards only)

Output Ratings +5V, Jumper selectable to 5 Amp or 1 Amp limit, higher than 5 Amp

current limit can be accommodated per user request. +3.3V @ 2.5 Amps if on-board regulator is used. +3.3V @ 5 Amps if system provides 3.3 Volts.

+VIO @ 1Amp. +/- 12V @ 1 Amp.

Drop Across the Switches 40 millivolts drop for every 1 Amp drawn for +5V, +3.3V and +VIO.

30 millivolts drop for every 1 Amp drawn for -12V.

30 millivolts drop for every 100 milliampere drawn for +12V.

**Propagation Delay:** Less than 500 pico-seconds from the PC bus to the UUT. The switch

propagation delay is rated at only 250 Pico-seconds.

**On-Off Controls:** SPST switch on-board, or the system parallel port.

**Outputs:**

J3 +5V, +12V and +3.3V current draw by the UUT can be measured at

a four-point terminal, J3, by a voltmeter. Each volt represents 1

Amp.

JP1-1 to JP1-59, all odd pins on the B side, 100 mil centers.

JP1 JP1-2 to JP1-60, all even pins on the B side, 100 mil centers.

JP2-1 to JP2-59, all odd pins on the A side, 100 mil centers.

JP2 JP2-2 to JP2-60, all even pins on the A side, 100 mil centers.

The signals at JP1 and JP2 are active when the extender power is on and tri-stated when the power is off. **Mechanical Dimensions:**

Height 4.5 inches

Length 6.8 inches

Bus: CPCI-64

CompactPCI 32 or 64 bit, system slot or adapter card.

Voltages:

Input requirement +5V at 200 ma, +/- 12V at 50 mA.

Inputs for UUT From PC bus or the external input, configurable jumpers per voltage.

Output Ratings +5V, Jumper selectable to 5 Amp or 1 Amp limit.

+3.3V @ 2.5 Amps. +VIO @ 1 Amp. +/- 12V @ 1 Amp.

Output Voltage Drop 40 millivolts drop for every 1 Amp drawn for +5V, +3.3V and +VIO.

30 millivolts drop for every 1 Amp drawn for -12V.

30 millivolts drop for every 100 milliampere drawn for +12V.

**Propagation Delay:** Less than 500 pico-seconds from the PC bus to the UUT. The switch

propagation delay is rated at only 250 Pico-seconds.

**ON-OFF Controls:** SPST switch on-board, or JPX.

**Outputs:**

J3 +5V, +12V and +3.3V current draw by the UUT can be measured at

a four-point terminal, J3, by a voltmeter. Each volt represents 1

Amp.

JTA-E All CompactPCI signals.

**Mechanical Dimensions:**

Height 8 inches Width 3.94 inches, 3U

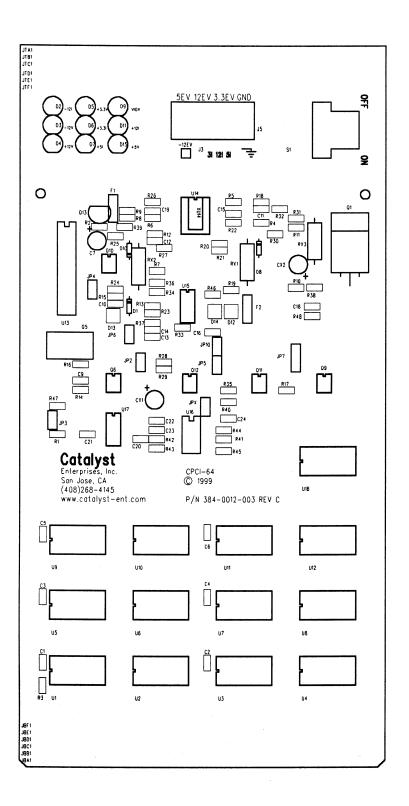

# **BOARD LAYOUT, PCIAX**

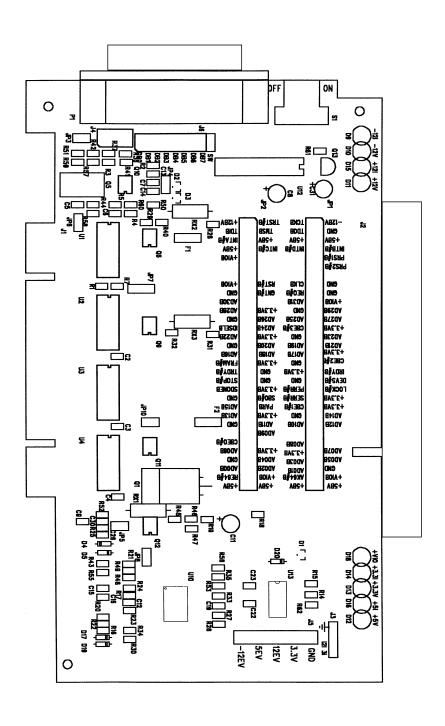

# **BOARD LAYOUT, CPCI-64**